# United States Patent 1191

## Tang

### [54] METHOD FOR SIMULTANEOUS **PROGRAMMING OF IN-SYSTEM PROGRAMMABLE INTEGRATED CIRCUITS**

- [75] Inventor: Howard Y. M. Tang, San Jose, Calif.

- [73] Assignee: Lattice Semiconductor Corporation, Hillsboro, Oreg.

- [21] Appl. No.: 505,837

- [22] Filed: Jul. 21, 1995

- [51] Int. Cl.<sup>6</sup> ...... H03K 19/177

- [52]

- Field of Search ...... 326/38, 39; 364/491, [58] 364/489, 490

### **References Cited** [56]

### **U.S. PATENT DOCUMENTS**

| 4,488,246 | 12/1984 | Brice 364/716   |

|-----------|---------|-----------------|

| 4,879,688 | 11/1989 | Turner et al    |

| 4,940,909 | 7/1990  | Mulder 326/38   |

| 5.237.218 | 8/1993  | Josephson et al |

US005635855A

### 5,635,855 **Patent Number:** [11]

#### [45] **Date of Patent:** Jun. 3, 1997

| 5,256,918 | 10/1993 | Suzuki 326/38      |

|-----------|---------|--------------------|

| 5,329,179 | 7/1994  | Tang et al 307/465 |

| 5,493,239 | 2/1996  | Zlotnick           |

| 5,495,181 | 2/1996  | Kolze 326/38       |

### OTHER PUBLICATIONS

ISP Manual 1994 "Lattice In-System Programmability Manual 1994".

Primary Examiner-Edward P. Westin

Assistant Examiner-Benjamin D. Driscoll Attorney, Agent, or Firm-Skjerven, Morrill, MacPherson, Franklin & Friel; Edward C. Kwok

### ABSTRACT [57]

Multiple in-system programmable devices are connected in series to a programming controller for simultaneous programming. One embodiment puts all such in-system programmable devices in programming mode, and to receive programming data and programming instruction simultaneously. In that configuration, all devices begins programming and stops programming simultaneously.

## 10 Claims, 24 Drawing Sheets

Program Command Generator

| SDI —   |                   |                                       |                   |     |

|---------|-------------------|---------------------------------------|-------------------|-----|

| 501     | 1                 | · · · · · · · · · · · · · · · · · · · |                   | SDO |

| Row 0   | Row Addr. 0       | Row O High                            | Row Addr. 0 High  | 1   |

| Row 1   | Row Addr. 1       | Row O Low                             | Row Addr. O Low   |     |

| •••     | DEVICE 401        | Device 402                            | DEVICE 403        |     |

| Row 43  | Row Addr. 43      | Row 21 Low                            | Row Addr. 21 Low  |     |

| Row 44  | Row Addr. 44      | Row 22 High                           | Row Addr. 22 High |     |

| Row 45  | Arch. Row 22 Low  | Row Addr. 22                          | 2 Low             | •   |

| Row 46  | Row 23 High       | Row Addr. 23 High                     |                   |     |

| •••     | DEVICE 402        | DEVICE 403                            |                   |     |

| Row 191 | Row 95 Low        | Row Addr. 95 Low                      |                   |     |

| Row 192 | Row Addr. 96 High | n                                     | - 、               |     |

| • • •   | DEVICE 403        |                                       | 900               |     |

| Row 215 | Row Addr. 107 Los | Η .                                   |                   |     |

QF5892\* G 0\* BIT F 0\* Ø NAnd Array Rows\* ROW ADDRESS 43 LOOOOO \_\_\_\_ ROW ADDRESS Ø 601 N Architecture Row\* BIT L 5808 131 10101010101010100000\* N UES Row\* L5828 10101011110011011110\* CFBD8\* AF2C

7a

FIG. 8a

| <br>FIG. 8b | FIG. 8d | TO FIG. 8 |

|-------------|---------|-----------|

| <br>FIG. Ba | FIG. Bc | KEY TO    |

|          | 0000000000000 •                  |

|----------|----------------------------------|

|          |                                  |

|          |                                  |

|          |                                  |

|          | 0000000-0000 •                   |

|          | 000-00                           |

|          | 00                               |

|          | 0                                |

|          | 00000-0000                       |

|          |                                  |

|          | 0000000000000                    |

|          |                                  |

|          |                                  |

|          |                                  |

|          | 00000000-0-0-                    |

|          | 00                               |

|          | 00                               |

|          |                                  |

|          |                                  |

|          | 00                               |

|          | 000000000000-00                  |

|          |                                  |

|          |                                  |

|          |                                  |

|          | 000000000-                       |

|          | 0000                             |

|          | 00                               |

|          | 0-0000000-                       |

|          | 00000000                         |

|          | 000000000                        |

| *        | 00000000000                      |

| 0        |                                  |

| 9 0      |                                  |

| 5 0      |                                  |

| 4 0      |                                  |

|          |                                  |

| L O O    |                                  |

| * 001    |                                  |

| •        | $\top$ $\checkmark$ $\downarrow$ |

|          |                                  |

| tentari. | S_S_                             |

|          | X A X                            |

FIG. 8b

|      | ROW<br>ADDRESS | HICH | MOT      | HIGH                           | LOW             | HICH       | LOW                                   | HIGH        | LOW   | HIGH         | LOW          | ••         |

|------|----------------|------|----------|--------------------------------|-----------------|------------|---------------------------------------|-------------|-------|--------------|--------------|------------|

|      |                | Ø    | Ø        |                                | -               | 2          | 7                                     | 3           | 3     | 4            | 4            | _          |

| 159  |                |      |          |                                |                 |            |                                       |             |       |              |              | 801        |

| BIT  |                | ]    |          |                                |                 |            |                                       |             | -     |              | <del>.</del> |            |

| ليها |                |      |          |                                |                 | -0         |                                       | 0-          |       | -0           |              |            |

|      |                | 00   |          |                                | · - +           |            | 00                                    |             | 00    |              |              |            |

|      |                |      | -  <br>- | . <del>4</del> 4               |                 | 00         | 101                                   | 0           | 101   | 00           | 00           | ·          |

|      |                | 01   | 000      | · + +<br>) + +                 | ·               | 00         | · • • • •                             | 0           | 100   | 00           |              |            |

|      |                |      |          |                                | ·               | · • •      |                                       |             | ,     | -0           |              | -0         |

|      |                |      |          | 00                             |                 |            | 00                                    |             | 0-    |              | 00           | <u>-  </u> |

|      |                |      | 00       | ) <del>-</del> +               |                 | ·          |                                       |             |       | 00           |              |            |

|      |                |      |          | , <del>An</del> én             | ·               | 00         |                                       |             |       |              | 000          |            |

|      |                |      |          | · • •                          | ·               |            | 10                                    | )           | · • • | 00           |              |            |

|      |                |      |          | )                              | ·               | 00         | • • • • • • • •                       | · • •       | 0-    | 00           | 00           |            |

|      |                | ōc   |          |                                | • • • •         | · <u>-</u> |                                       | 0-          |       | 00           |              | 0          |

|      |                |      |          |                                | 00              | 00         |                                       | · • •       | · 4 4 | 00           |              |            |

|      |                | 00   |          | ) <del></del><br>) <del></del> | · • •           | ·          | 10                                    | 010         |       | 00           | 000          | <u>}</u>   |

|      |                |      | - <br>-  | ·                              | ·               | 00         | -00                                   | 00          | )     |              | 00           | 2          |

|      |                |      |          |                                | • • • •         | 00         |                                       | 0-          |       | 0-           |              | 0          |

|      |                |      |          | · •                            | · • •           |            |                                       | -0          | 00    | 100          |              |            |

|      |                | 00   |          | 00                             | · • •<br>• • •  | · • •      | 100                                   | • • • • • • |       | 000          | 000          |            |

|      |                |      |          | · • •                          | 00              | 0-         | 0                                     | ,           |       | 00           |              |            |

|      |                | οċ   |          | ,                              | - <del>-</del>  |            | 00                                    | õõ          | -0    | 1 <b>4 4</b> | 0            | •          |

|      |                |      |          | · • •                          | · • •           |            | 00                                    |             |       | 000          |              |            |

|      |                | 0.0  | 010      | ·                              | · • •           | 00         | · · · · · · · · · · · · · · · · · · · |             |       | 00           | 50           |            |

|      |                |      |          | · •                            | • • • • • • • • |            | · • •                                 |             | 0-    | -0-          |              |            |

|      |                |      |          | 00                             | )               | 0-         | 00                                    |             | 0-    |              | 00           |            |

| • • • • • • •                         |                                         |

|---------------------------------------|-----------------------------------------|

| · · · · · · · · · · · · · · · · · · · | •                                       |

| • • • • • • • • • •                   | •                                       |

| · • • • • • • • •                     | • 00-0 >                                |

| • •                                   | • • • • • • • • • • • • • • • • • • • • |

| • • • • • • • •                       | • *** *** *** *** *** *** *** *** *** * |

| • • • • • • • •                       | C+000000 E++                            |

| • • • • • • • • • • •                 | •                                       |

| • + +                                 | ·                                       |

| • •                                   | +                                       |

| • • • • • •                           |                                         |

| • •                                   |                                         |

| • • • • • • •                         |                                         |

|                                       | <u></u>                                 |

| A d d d                               | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~  |

| **** **** **** ****                   |                                         |

|                                       |                                         |

|                                       |                                         |

|                                       |                                         |

|                                       | 0                                       |

| I                                     |                                         |

| 1                                     | 0-0000000                               |

|                                       | ~~~~~ 0~0~~~~~~~~~~~~~~~~~~~~~~~~~~~~~  |

|                                       | 0                                       |

|                                       | 0+++++++++++++++++++++++++++++++++++++  |

|                                       |                                         |

|                                       | v                                       |

|                                       |                                         |

|                                       |                                         |

|                                       |                                         |

| · · · · · · · · · · · ·               |                                         |

|                                       | MO                                      |

| * * *                                 |                                         |

|                                       | CO                                      |

|                                       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~  |

|                                       | 0                                       |

| 4 4 4                                 |                                         |

| 4 4 4 4                               |                                         |

|                                       |                                         |

| · ~~~~                                |                                         |

|                                       |                                         |

| ALL<br>ROW<br>ROW                     |                                         |

|                                       |                                         |

| -                                     |                                         |

FIG. 8d

| HICH                                    | Ň                          | 풍           | N           | 퐀                 | X           | ¥                | 3              | 퐀           | ×           |                   |

|-----------------------------------------|----------------------------|-------------|-------------|-------------------|-------------|------------------|----------------|-------------|-------------|-------------------|

| . Ŧ                                     | NO1.                       | •<br>HICH   | NOT         | Ĕ                 | D           | Η̈́              | LOW            | HOH         | LO1         |                   |

| 64                                      | 64                         | 104         | 4           | 105               | 105         | 90               | 106            | 107         | 101         |                   |

| Ģ                                       | Ģ                          | ž           | Ę           | ¥                 | Ę           | ₽                | 10             | 1           | 10          |                   |

|                                         |                            |             |             |                   |             |                  |                |             |             |                   |

|                                         |                            |             |             |                   |             |                  | •              |             |             |                   |

|                                         |                            |             |             |                   | 00          |                  | 00             |             | 0*          |                   |

|                                         |                            |             |             |                   | 55          | 1                |                |             |             |                   |

| · · · · ·                               |                            | ·           |             |                   |             | · <del>4</del> 4 |                |             |             |                   |

|                                         |                            | **** ****   |             |                   | 00          |                  | -0             |             |             |                   |

|                                         | <b></b>                    |             |             | · • • • • • • • • |             |                  |                |             | 00          |                   |

| *                                       | A                          | <b></b>     |             |                   | • • ••      | <b>***</b>       | · • •          | 00          |             |                   |

| 4 4                                     |                            |             |             |                   |             |                  | ·              |             |             |                   |

|                                         |                            |             |             |                   |             |                  | 00             |             |             |                   |

| • •                                     | <b>****</b>                | 4 4         |             | <del>~~</del> ~~  | -           | <del></del>      |                |             | 00          |                   |

|                                         | 4 A                        |             |             |                   | 00          |                  |                |             |             |                   |

| • • <del></del>                         | <b>***</b> ***             | <del></del> |             |                   | 00          |                  |                |             |             |                   |

|                                         |                            |             | -0          |                   | <del></del> | <del></del>      |                |             |             |                   |

| • • •                                   |                            |             | • •         | 2-                |             |                  | * *            |             |             |                   |

| <del></del>                             | <b>****</b> ****           | • •         |             | <del></del>       |             |                  | <b></b>        |             |             |                   |

|                                         | *                          |             |             |                   |             |                  | 101            |             |             |                   |

|                                         | <del></del>                | -           |             |                   |             |                  |                |             |             |                   |

|                                         | <b>***</b> ****            | **** ****   |             | -0                | 00          |                  | 4 4            |             |             |                   |

|                                         | danış danış<br>danış danış |             |             |                   | 20          |                  |                | 2-          |             |                   |

| · · · · · · · · · · · · · · · · · · ·   |                            |             | -0          |                   |             |                  | •              | <del></del> |             | <b>*</b>          |

|                                         |                            |             |             | 22                |             |                  |                |             |             | <b>****</b> ***** |

| · • •                                   |                            |             |             |                   |             |                  |                |             |             |                   |

|                                         |                            | *           | <del></del> |                   |             | 00               | <del></del>    |             | <del></del> | <b>****</b>       |

|                                         |                            |             | •           |                   |             |                  | 10             |             |             | *                 |

|                                         |                            | · · ·       |             | -0                |             |                  |                |             |             | 4 4               |

|                                         | •••• • • •                 |             | <b>4 4</b>  | * *               | <del></del> |                  | <del>~ ~</del> |             | -0          |                   |

| · • • • • • • • • • • • • • • • • • • • |                            | 10          | <b>4 4</b>  | <u></u>           | 00          |                  |                |             |             |                   |

|                                         | * *                        |             |             |                   | <del></del> |                  |                |             |             | *****             |

|                                         |                            |             | <b>*</b> *  | -0                |             |                  | • •            |             | -           | <u> </u>          |

|                                         |                            | ·           |             |                   |             |                  |                |             |             | E                 |

G

| SDI•           | SD0                                          |

|----------------|----------------------------------------------|

| 8 Bit ID       | 00001000 0000001 00000011                    |

| Bulk Erase     | 00011 00011 00011                            |

| Shift Addr.    | 01110 00001 00001                            |

| Addr. Bits     | 000 • • • • 0001 000 • • • • • • 0001        |

| Shift Data In  | 00010 00010 00010                            |

| Data Bits      | 000000 000 111111 110111 000 110111000       |

| Program        | 00111 00111 00111                            |

| Verify         | 01010 01010 01010                            |

| Shift Data Out | 00010 00010 00010                            |

| Shift Data In  | 00010 00010 00010                            |

| Data Bits      | 000001 000 111111 100101 111 100111011 10111 |

| Program        | 00111 01000 01000                            |

| Verify         | 01010 01011 01011                            |

| Shift Data Out | 00010 00010 00010                            |

| Shift Addr.    | 01110 00001 00001                            |

| Addr. Bits     | 000 · · · · · 0010 000 · · · · · · 0010      |

| Shift Data In  | 00010 00010 00010                            |

| Data Bits      | 000010 000 111111 110111000 110111000 10001  |

| Program        | 00111 00111 00111                            |

| Verify         | 01010 01010 01010                            |

| Shift Data Out | 00010 00010 00010                            |

| Shift Data In  | 00010 00010 00010                            |

| Data Bits      | 000011 000 111111 100101 111 100111011 10111 |

| Program        | 00111 01000 01000                            |

| Verify         | 01010 01011 01011                            |

| Shift Data Out | 00010 00010 00010                            |

|                |                                              |

|                | <u>i</u>                                     |

| Shift Data In  | 01110 01110 00010                            |

| Data Bits      | 100111011 10111                              |

| Program        | 00000 00000 01000                            |

| Verify         | 00000 00000 01011                            |

| Shift Data Out | 01110 01110 00010 FIG. 10a                   |

|                |                                              |

-1000

8 Bit ID **Bulk Erase** Shift Addr. Addr. Bits Shift Data In Data Bits Program Verify Shift Data Out Shift Data In Data Bits Program Verify Shift Data Out Shift Addr. Addr. Bits Shift Data In Data Bits Program Verify Shift Data Out Shift Data In Data Bits Program Verify Shift Data Out Addr. Bits Shift Data In Data Bits Program Verify

Program Verify Shift Data Out Shift Data In Data Bits Program Verify Shift Data Out

|       |         |      |      |            |       |     |       |    | ,     | - 1000 | J    |

|-------|---------|------|------|------------|-------|-----|-------|----|-------|--------|------|

| Dev 1 | ID De   | v 2  | ID   | Dev        | 13    | ID  |       | 1  | •     |        |      |

| Erase | Erase   | Era  |      |            | 002   |     |       |    |       |        |      |

| Pass  | Shift   | Shif | t    | -1         | 003   |     |       |    |       |        |      |

| Dev 2 | Addr.   | 0    |      | Dev        | / 3   | Add | ir. 0 |    | 7-1   | 004    |      |

| Shift | Shift   | Shi  | ft   | -1         | 005   |     |       |    |       |        |      |

| Dev 1 | Addr.0+ | Data | i    |            | Dev   | 2   | Addr0 | Hi | Dev 3 | Addr.  | 0 Hi |

| Prog. | Prog.   | Pro  | og.  | -1         | 007   |     |       |    |       |        |      |

| Ver.  | Ver H   | Ver  | Η    | -1         | 800   |     |       |    |       |        | 1006 |

| Shift | Shift   | Shi  | ft   | <b>r</b> ' | 009   |     |       |    |       |        |      |

| Shift | Shift   | Shi  | ft   | -1         | 010   |     |       | _  |       |        |      |

| Dev 1 | Addr.   | 1+[  | )ata |            | De    | v 2 | Addr0 | Lo | Dev 3 | Addr.  | O Lo |

| Prog. | Prog.   | Pro  | og.  |            | 012   |     |       |    |       |        | 1011 |

| Ver.  | Ver L   | Ver  | L    | -1         | 013   |     |       |    |       |        | 1011 |

| Shift | Shift   | Shi  | ft   | -1         | 014   |     |       |    |       |        |      |

| Pass  | Shift   | Shi  | ft   |            |       |     |       |    | _     |        |      |

| Dev 2 | Addr.   | 1    |      | Der        | 13    | Ado | dr. 1 |    |       |        |      |

| Shift | Shift   | Shi  | ft   |            |       |     |       |    |       |        |      |

| Dev 1 | Addr.2  | +Dat | a    |            | De    | v 2 | Addr1 | Hi | Dev 3 | Addr.  | 1 Hi |

| Prog. | Prog.   | Pr   | og.  |            | - · · |     |       |    |       |        |      |

| Ver.  | Ver H   | Ver  | ·H   |            |       |     |       |    |       |        |      |

| Shift | Shift   | Shi  | ft   |            |       |     |       |    |       |        |      |

| Shift | Shift   | Shi  | ft   |            |       |     |       |    |       |        |      |

| Dev 1 | Addr.3  | +Dat | ۵    |            | De    | v 2 | Addr1 | Lo | Dev 3 | Addr.  | 1 Lo |

| Prog. | Prog.   | Pr   | og.  |            |       |     |       |    |       |        |      |

| Ver.  | Ver L   | Ver  | L    |            |       |     |       |    |       |        |      |

| Shift | Shift   | Sh   | ft   |            |       |     |       |    |       |        |      |

|       |         |      |      | 1          |       |     |       |    |       |        |      |

|       |         |      |      | į          |       |     |       | -  |       |        |      |

|       | Pass    | Shi  |      |            |       |     |       |    |       |        |      |

| Dev   | _       | _    | 107  |            |       |     |       |    |       |        |      |

| Shift | Shift   | Sh   |      |            | _     |     |       |    |       |        |      |

|       | Addr.   |      | 7    | Hi         |       | -   |       |    |       |        |      |

| Nop   | Nop     |      | og.  |            |       |     |       |    |       |        |      |

| Nop   | Nop     |      | r H  | 1          |       |     |       |    |       |        |      |

| Pass  | Pass    | Sh   |      | 1          |       |     |       |    |       |        |      |

| Pass  | Pass    | Sh   |      | 1          |       |     |       |    | FIG.  | 10b    |      |

| Dev 3 | 1       | -    | )7   | Lo         |       |     |       |    |       |        |      |

| Nop   | Nop     |      | og.  | 4          |       |     |       |    |       |        |      |

| Nop   | Nop     | Ver  | -    | 1          |       |     |       |    |       |        |      |

| Pass  | Pass    | Sh   | ift  | J          |       |     |       |    |       |        |      |

|       |         |      |      |            |       |     |       |    |       |        |      |

# **U.S. Patent**

ispGAL Programming State Machine Instruction Set

| Instruction | Operation          | Description                                                                               |

|-------------|--------------------|-------------------------------------------------------------------------------------------|

| 00000       | NOP                | No Operation Performed.                                                                   |

| 00010       | SHIFT_DATA         | Clocks Data Into, Or Out Of, The Data Shift Register.                                     |

| 00011       | BULK_ERASE         | Erases The Entire Device.                                                                 |

| 00111       | PROGRAM            | Programs The Serial Shift Register Data Into The Addressed Row.                           |

| 01010       | VERIFY             | Load Data From The Selected Row Into The Serial Shift Register.                           |

| 01110       | FLOWTHRU<br>(PASS) | Disables The Shift Register (SDI=SDO).                                                    |

| 10100       | ARCH SHIFT         | Enables The Architecture Shift Register For Shifting Data Into Or<br>Out Of The Register. |

# FIG. 10c

ispLSI Programming State Machine Instruction Set

| Instruction | Operation          | Description                                                                                                                             |

|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 00000       | NOP                | No Operation Performed.                                                                                                                 |

| 00001       | ADDSHIFT           | Address Register Shift: Shifts Address Into The Address Shift<br>Register From SDIN.                                                    |

| 00010       | DATASHIFT          | Data Register Shift: Shifts Data Into Or Out Of The Data Serial<br>Shift Register.                                                      |

| 00011       | UBE                | User Bulk Erase: Erase The Entire Device.                                                                                               |

| 00111       | PRGMH              | Program High Order Bits: The Data In The Data Shift Register is<br>Programmed Into The Addressed Row's High Order Bits.                 |

| 01000       | PRGML              | Program Low Order Bits: The Data In The Data Shift Register is<br>Programmed Into The Addressed Row's Low Order Bits.                   |

| 01001       | PRGMSC             | Program Security Cell: Programs The Security Cell Of The Device.                                                                        |

| 01010       | Ver/LDH            | Verify/Load High Order Bits: Load The Data From The Selected<br>Row's High Order Bits Into The Data Shift Register For<br>Verification. |

| 01011       | VER/LDL            | Verify/Load Low Order Bits: Load The Data From The Selected<br>Row's Low Order Bits Into The Data Shift Register For<br>Verification.   |

| 01110       | FLOWTHRU<br>(PASS) | Flow Through: Bypasses All The Internal Shift Registers And SDOUT Becomes The Same As SDIN.                                             |

FIG. 10d

## U.S. Patent

## **METHOD FOR SIMULTANEOUS PROGRAMMING OF IN-SYSTEM PROGRAMMABLE INTEGRATED CIRCUITS**

### BACKGROUND OF THE INVENTION

## 1. Field of the Invention

This invention relates to programmable integrated circuits, and in particular, the present invention relates to techniques for programming multiple programmable devices simultaneously.

2. Discussion of the Related Art

Programmable devices that can be programmed and reprogrammed without being removed from its application environment are widely preferred because programming and reprogramming of such devices can be performed with ease. 15 One type of such devices is the "In-system programmable logic devices" or "ISP PLDs", available from Lattice Semiconductor Corporation. (To simplify reference, in the following description, such and similar devices are all referred to as "ISP PLDs". It should be understood, however, that the 20 teachings in the following description are applicable to all types of field programmable devices, including programmable logic devices, programmable memories, and programmable analog circuits). The design and use of ISP PLDs are disclosed in the prior art, e.g. (i) U.S. Pat. No. 5,329,179 25 entitled "Arrangement For Parallel Programming Of In-system Programmable IC Logical Devices", to Tang et al, filed on Oct. 5, 1992 and issued on Jul. 12, 1994. (ii) U.S. Pat. No. 5,237,218, entitled "Structure and Method for Multiplexing Pins for In-system Programming", to G. 30 Josephson et al, filed on May 3, 1991 and issued on Aug. 13, 1993; (iii) U.S. Pat. No. 4,879,688, entitled "In-system Programmable Logic Devices" to Turner et al, filed on May 13, 1986, issued on Nov. 7, 1989; and (iv) U.S. Pat. No. 4,855,954, entitled "In-system Programmable Logic Device 35 with Four Dedicated Terminals" to Turner et al, filed on Oct. 25, 1988, and issued on Aug. 8, 1989.

In the prior art, each ISP PLD in a system board containing multiple ISP PLDs is individually and sequentially programmed. To program multiple ISP PLDs simulta- 40 neously requires both additional hardware and special configurations of the ISP PLDs. For example, where simultaneous programming of multiple ISP PLDs is possible, additional circuits for signal multiplexing are typically required. When devices in an application are programmed 45 individually and sequentially, the devices to be programmed are chained serially and hence the total programming time of the serial chain of devices is the sum of the times required to program each device individually.

An ISP PLD contains a large number of programmable 50 logic components, e.g. the "min-terms" of a programmable gate array. In some ISP PLDs, a linear address space is provided, and the programmable logic components of an ISP PLD are programmed in ascending address order until all the programmable logic components of the entire ISP PLD are 55 programmed. Thus, even when simultaneous programming is provided, the total programming time of a system board is often determined by the sum of the time required to program that ISP PLD on the system board which has the most number of programmable components, and the time 60 required to send data to all the ISP PLDs of the serial chain.

In the prior art, a "programming command generator" is given a data file which contains only the pattern necessary to program the ISP PLDs on a given system board. The programming command generator derives from the data file 65 all the device dependent parameters, and provides the commands for the programming to occur.

### SUMMARY OF THE INVENTION

In accordance with the present invention, a method for programming, simultaneously, multiple field programmable integrated circuits or devices is provided. According to the present invention, such method includes the steps of: (i) connecting field programmable devices serially in a chain configuration; (ii) constructing a data stream file which contains a data stream for programming the field programmable devices simultaneously, such that the programmable 10 devices are simultaneously scheduled under the data stream (a) to receive instructions, (b) to shift programming data into the field programmable devices, (c) to execute instructions and (d) to shift data out of the field programmable devices; (iii) retrieving from each of a number of program data files, for each of the field programming devices, an individual programming data stream; (iv) filling the data stream file with programming data from each of the individual programming data streams thus retrieved; and (v) programming the field programmable devices simultaneously using the data stream file thus composed.

In accordance with a further aspect of the present invention, the individual programming data stream includes programming instructions and programming data. Under this further aspect, programming data are sorted such that rows having a predetermined data pattern (e.g. all '1's) are placed behind rows not having the predetermined data pattern. In one embodiment, the predetermined data pattern corresponds to a default data pattern of the field programmable device when it is unprogrammed. In accordance with the present invention, programming for such rows can be omitted.

The present invention achieves the advantage of programming simultaneously the devices in a serially connected chain of field programmable devices, thereby minimizing total programming time. The present invention achieves such advantage using conventional programming hardware without requiring additional circuitry.

In accordance with one aspect of the present invention, the devices programmed by the method of the present invention are not necessarily programmed in ascending or descending address order. By grouping programming data units (e.g. rows) in accordance to whether a predetermined pattern exists in the programming data in a given programming unit, so as to allowed such programming unit to be omitted, minimum programming time can be realized. In the present invention, substantial savings in programming time can be achieved by omitting programming in such programming unit having such predetermined data pattern.

The present invention further reduces programming time by lining up the addresses of rows which do not require programming.

This invention simplifies the software program portion of a programming command generator by the use of a composite file (ispSTREAM file) which includes the ID stream, the address stream, the instruction stream and the programming data stream. When applying these data streams to multiple ISP PLDs simultaneously, set-up times of the serially connected ISP PLDs are common, thereby achieving substantial savings in programming time.

In accordance with yet another aspect of the present invention, a data file is prepared representing a data stream including programming data bit patterns, programming addresses and programming instructions. Preparation of such a data file simplifies the task for the Programming Command Generator.

The present invention is better understood upon consideration of the detailed description below and accompanying drawings.

## BRIEF DESCRIPTION OF THE DRAWINGS

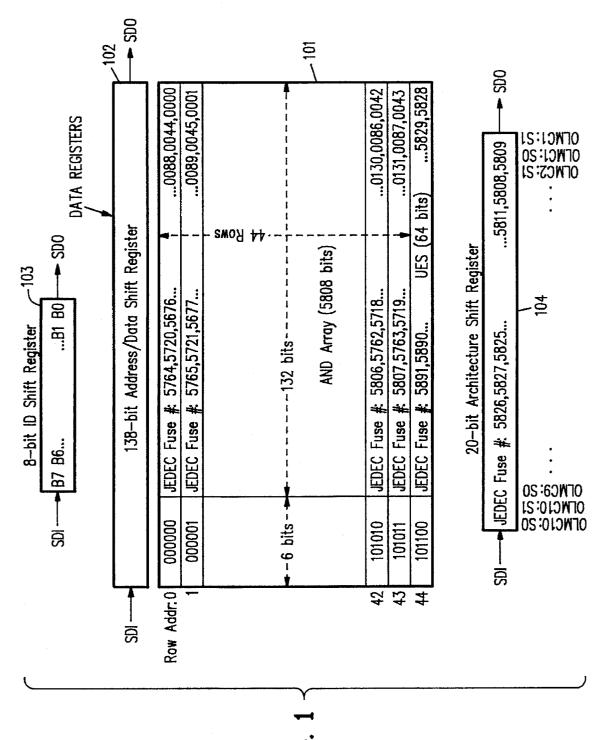

FIG. 1 shows an array map of an ispGAL22V10 device.

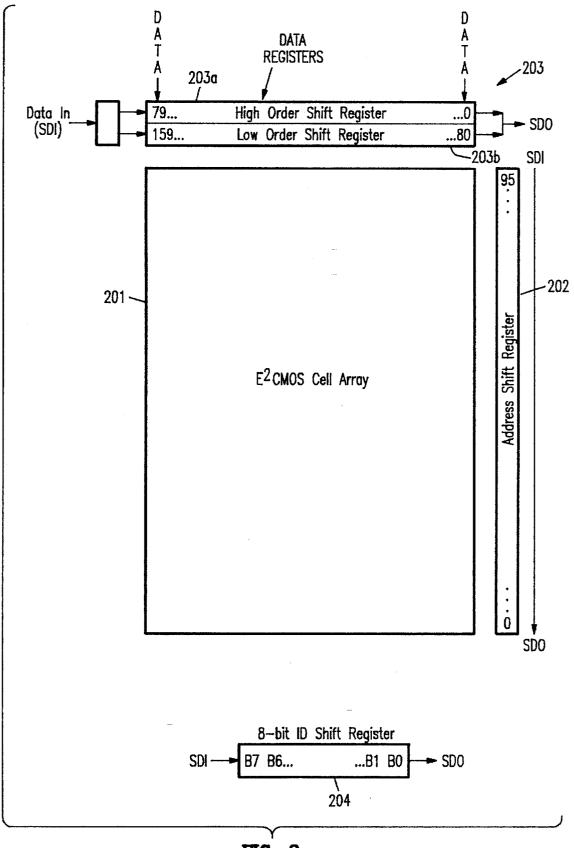

FIG. 2 shows an array map of an ispLSI 1016 device.

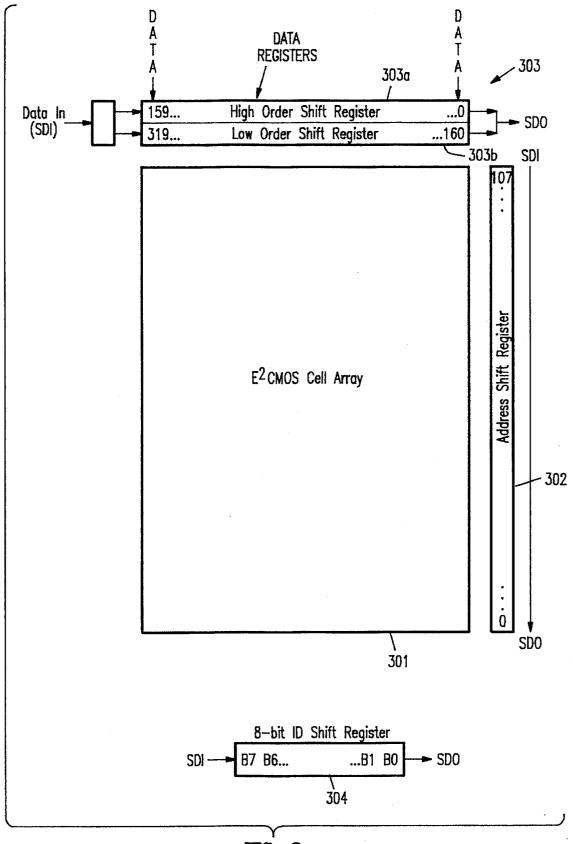

FIG. 3 shows an array map of an ispLSI 1032 device.

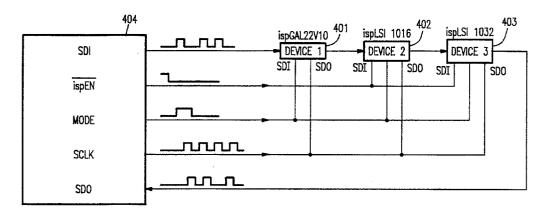

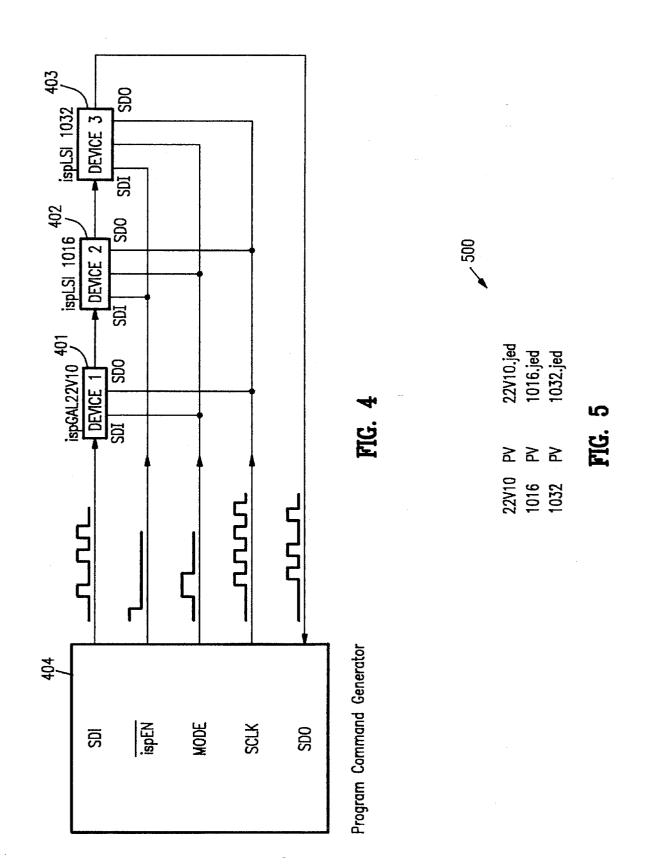

FIG. 4 shows an embodiment of the present invention in which three ISP PLDs 401, 402 and 403 are connected to a programming command generator 404.

FIG. 5 shows a configuration description file 500 for specifying programming of the ISP PLDs 401, 402 and 403 <sup>10</sup> of FIG. 4.

FIG. 6 is a JEDEC file illustrative of the "22V10.jed" file referenced in FIG. 5 for ISP PLD 401.

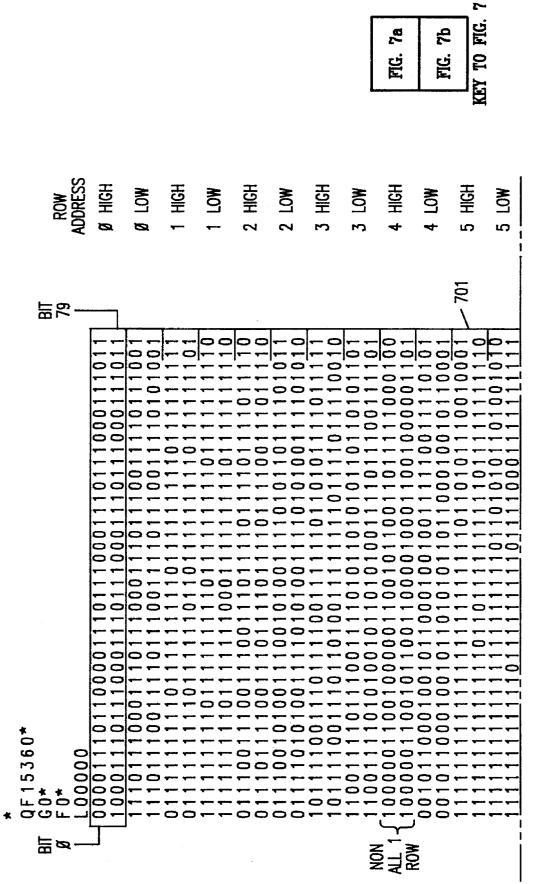

FIG. 7 is a JEDEC file illustrative of the "1016.jed" file  $_{15}$  referenced in FIG. 5 for ISP PLD 402.

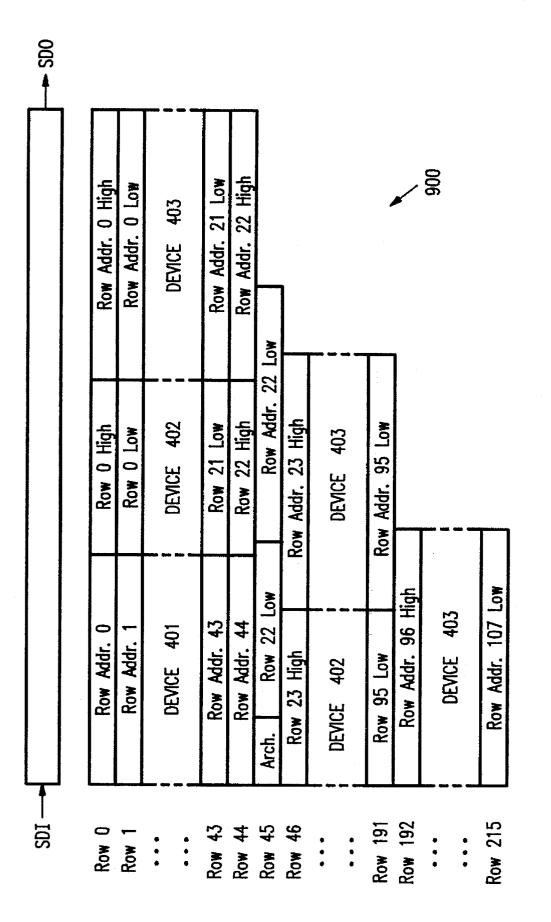

FIG. 8 is a JEDEC file illustrative of the "1032.jed" file referenced in FIG. 5 for ISP PLD 403.

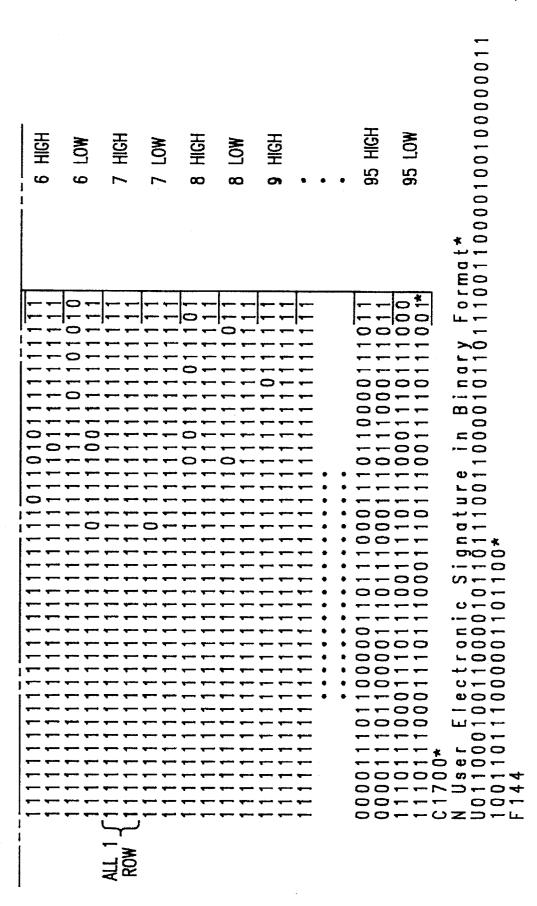

FIG. 9 illustrates the composite array map for serially connected chain 400 of FIG. 4.

FIG. 10*a* shows actual instructions and program data bits, which are derived from the JEDEC files of FIGS. 6–8, provided to ispSTREAM file 1000 of FIG. 10*b* below.

FIG. 10b shows the format of an ispSTREAM file 1000 25 for serially connected chain 400 of FIG. 4; serially connected chain 400 includes PLD ISPs 401, 402 and 403.

FIG. 10c shows the instruction set executable by the programming state machine of an ispGAL22V10 type device.

FIG. 10*d* shows the instruction set executable by the programming state machine of an ispLSI type device.

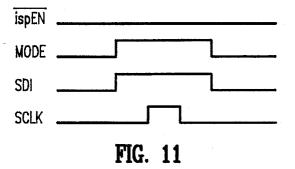

FIG. 11 is a signal protocol diagram showing transitions of signals ispEN, MODE, SCLK, and SDI when placing an ISP PLD into a "shift" state or an "execute" state.

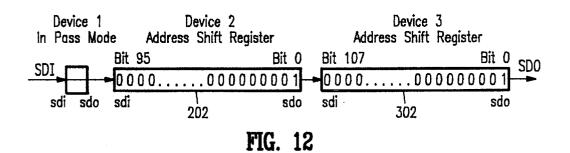

FIG. 12 is a schematic diagram showing address bits that are shifted into shift address registers 202 and 302.

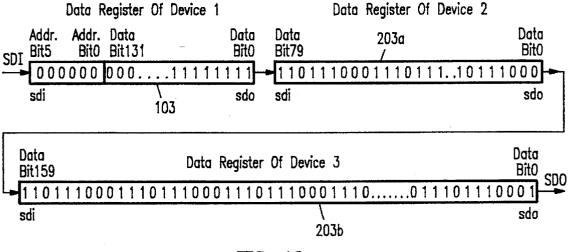

FIG. 13 shows the contents of data registers 103, 203a and 303a, after executing step 1516 illustrated in FIG. 15c.

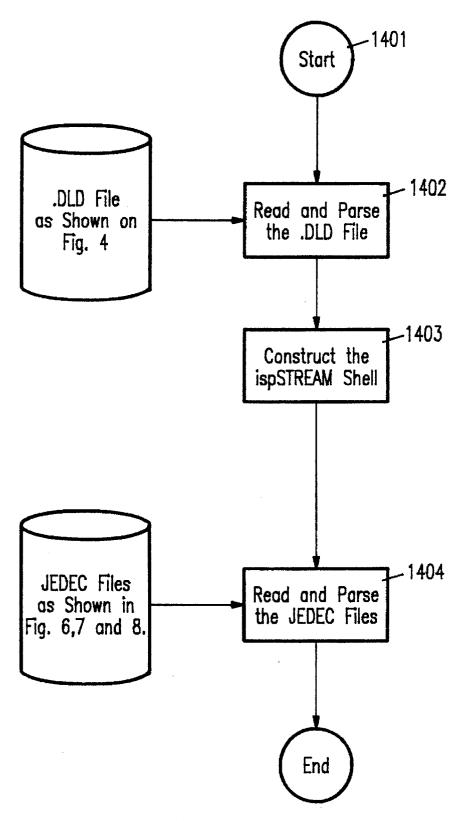

FIG. 14 is a flow diagram 1400 illustrating the creation of an ispSTREAM file in accordance with the present invention.

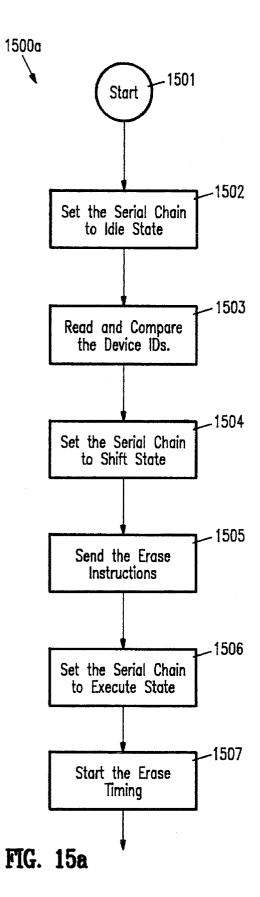

FIGS. 15*a* shows a portion 1500*a* of a flow diagram 1500, which shows a method for processing and downloading data 45 of ispSTREAM file 1000 to target devices of serially connected chain 400 of FIG. 4.

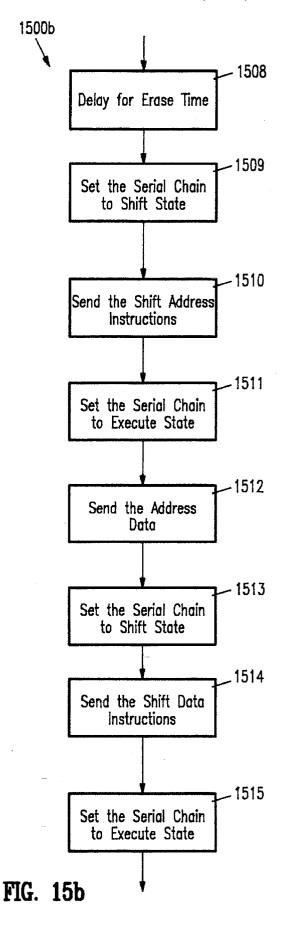

FIGS. 15b shows a portion 1500b of a flow diagram 1500, which shows a method of processing and downloading data of ispSTREAM file 1000 to target devices of serially con-<sup>50</sup> nected chain 400 of FIG. 4.

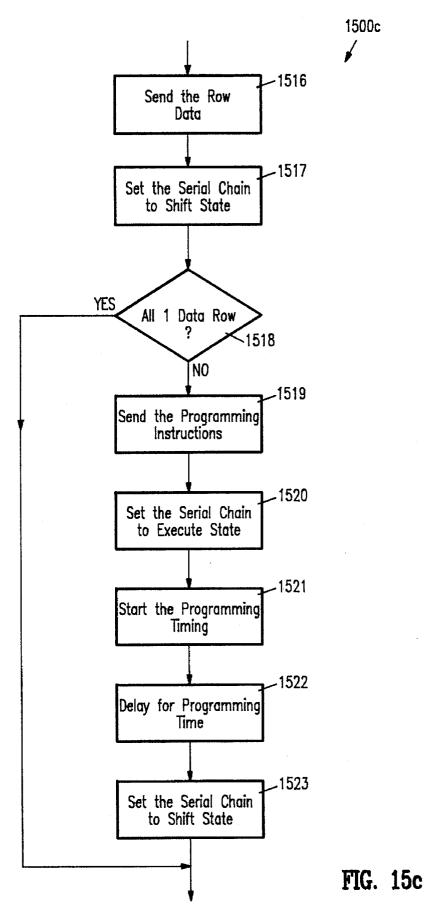

FIGS. 15c shows a portion 1500c of a flow diagram 1500, which shows a method for processing and downloading data of ispSTREAM file 1000 to target devices of serially connected chain 400 of FIG. 4.

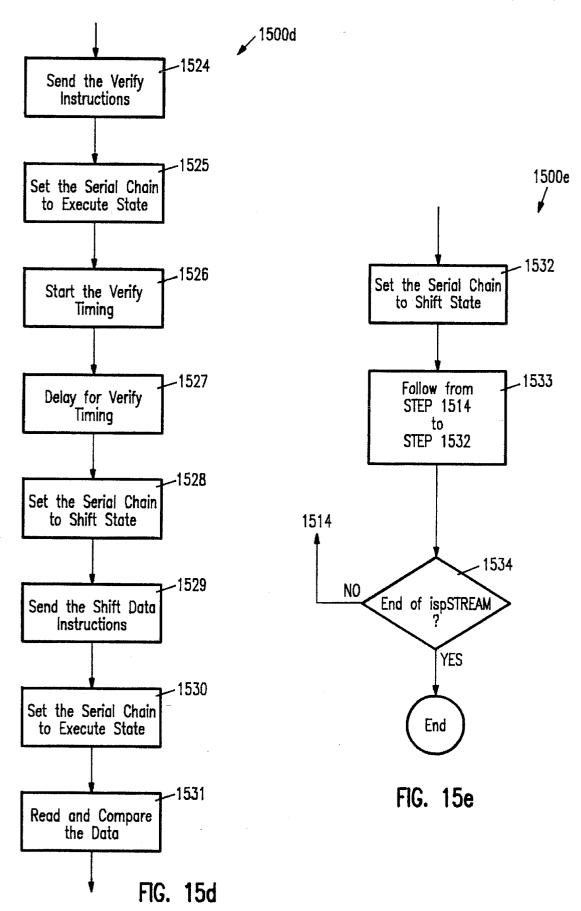

FIGS. 15d shows a portion 1500d of a flow diagram 1500, which shows a method for processing and downloading data of ispSTREAM file 1000 to target devices of serially connected chain 400 of FIG. 4.

FIGS. 15e shows a portion 1500e of a flow diagram 1500, which shows a method for processing and downloading data of ispSTREAM file 1000 to target devices of serially connected chain 400 of FIG. 4.

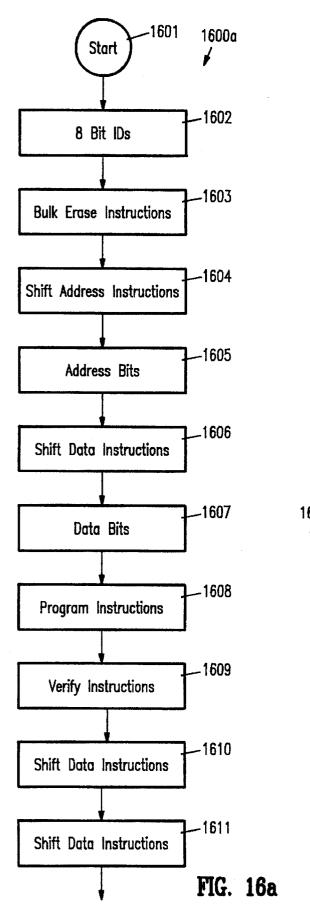

FIG. 16*a* is a portion 1600*a* of a flow diagram 1600 which 65 illustrates allocation of the ispSTREAM file 1000 shown in FIGS. 10*a* and 10*b*.

FIG. 16b is a portion 1600b of a flow diagram 1600 which illustrates allocation of the ispSTREAM file 1000 shown in FIGS. 10a and 10b.

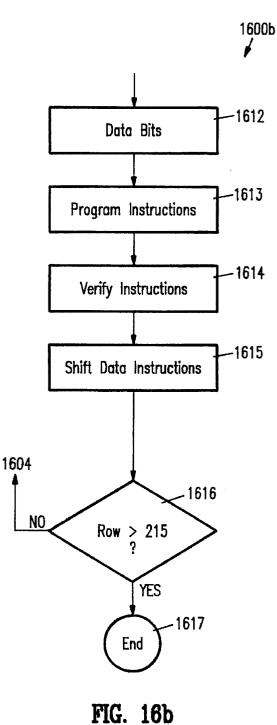

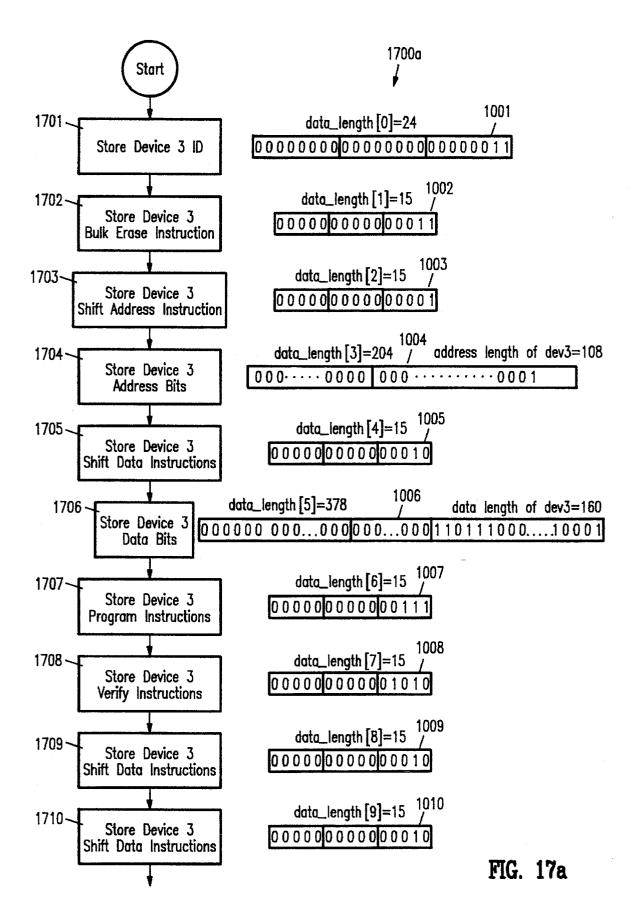

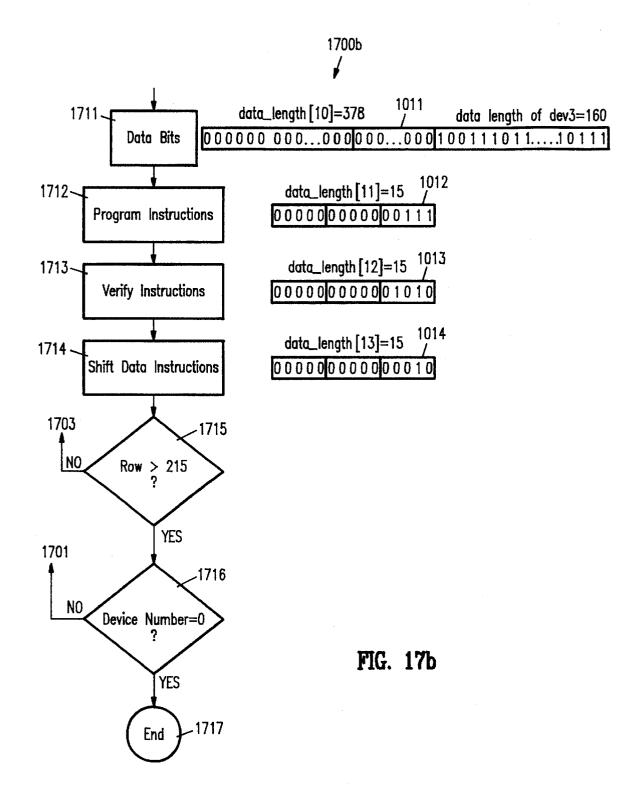

FIG. 17a shows, as a portion 1700a of a flow diagram

<sup>5</sup> 1700, on the left hand side, steps 1701–1714 taken to fill program data into ispSTREAM file 1000 and, on the right side, actual program data which are filled into data structures 1001–1014 of ispSTREAM file 1000 shown in FIG. 10b.

FIG. 17b shows, as a portion 1700b of a flow diagram 1700, on the left hand side, steps 1701–1714 taken to fill program data into ispSTREAM file 1000 and, on the right side, actual program data which are filled into data structures 1001–1014 of ispSTREAM file 1000 shown in FIG. 10b.

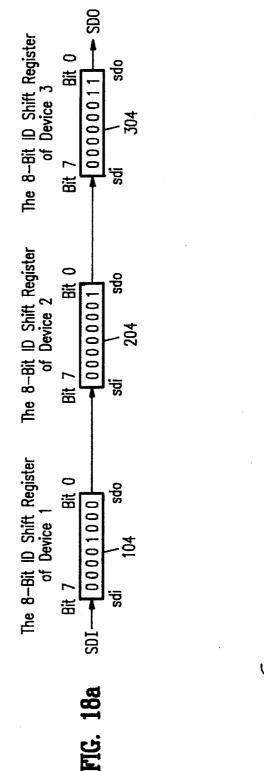

FIG. 18*a* shows the states of the three ID registers 104, 204 and 304 in ISP PLDs 401, 402 and 403 of serially connected chain 400.

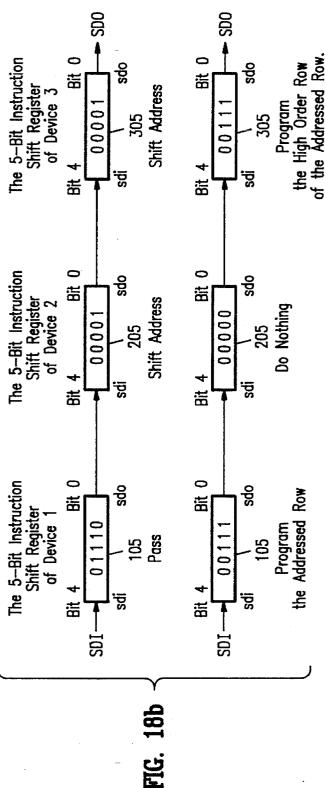

FIG. 18b shows the contents of 5-bit instruction registers 105, 205 and 305 of ISP PLDs 401-403, respectively, after 20 the shift address instructions are downloaded at step 1510.

FIG. 18c shows the contents of 5-bit instruction registers 105, 205 and 305 of ISP PLDs 401-403, respectively, after the programming instructions are downloaded at step 1519.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

One embodiment of the present invention, which is described in detail below, is provided by a software program written in the familiar "C" programming language. This software program, which is subject to copyright protection, is provided in source code form in the accompanying Appendix A. While the copyright owner permits anyone to make facsimile copies of this source code, as it appears in the files of the U.S. Patent and Trademark Office in connection with this patent document or patent disclosure, the copyright owner explicitly reserves all other rights with respect to this software program.

The present invention is described herein by reference to two types of ISP PLDs, both available from Lattice Semiconductor Corporation, the Assignee of this Patent Application. The first ISP PLD type is represented by the ispGAL22V10, which includes four programming pins: Mode, SCLK (Serial Clock), SDI (Serial Data In), and SDO (Serial Data Out). The operations of these programming pins are described in the "ISP Manual 1994", available from Lattice Semiconductor Corporation. The ispGAL22V10 device is placed in the programming mode when the Mode signal is asserted, while the signal on the SCLK pin is pulsed. Once in the programming mode, programming operations are controlled by the programmer via signals on the Mode and SDI pins.

The second ISP PLD type is the Lattice ispLSI devices. In the ispLSI devices, an ISP PLD is programmed using five 55 pins, which are designated: ispEN ("in-system programming Enable"), Mode, SCLK, SDI, and SDO. Unlike a ispGAL22V10 type device, an ispLSI type device is placed in the programming mode when the ispEN pin is asserted. Once in the programming mode, programming is controlled 60 by the Mode, SDI and SCLK pins. The structures and operations of ispLSI devices are also fully described in the ISP Manual 1994 referenced above.

FIG. 4 shows an embodiment of the present invention in which three ISP PLDs 401, 402 and 403 are connected to a programming command generator 404. As shown in FIG. 4, ISP PLD 401, 402 and 403 have their SDI and SDO terminals connected in a serial fashion ("serial chain" 400),

so that serial programming data from programming command generator 404 to ISP PLD 403 can be provided via the SDI and SDO terminals of ISP PLDs 401 and 402. Likewise, serial programming data can be shifted into ISP PLD 402 through the SDI and SDO terminals of ISP PLD 401. This serial connection is known as a "serial chain". In this embodiment, ISP PLD 401 is an ispGAL22V10 device, ISP PLD 402 is an ispLSI type device (specifically, an ispLSI 1016) and ISP PLD 403 is also an ispLSI type device (an ispLSI 1032). The Mode and SCLK pins of ISP PLDs 401, 10 dldfile". In FIG. 14, execution of subroutine "dl\_read\_ 402 and 403 are commonly connected. In addition, the ispEn pins of ISP PLDs 402 and 403 are commonly connected.

FIG. 1 shows an array map of the ispGAL22V10 device. As shown in FIG. 1, an ispGAL22V10 device is programmed by setting programmable fuses for a  $44 \times 132$ -bit 15 configuration description file 500 includes 3 lines of text, AND array and a 64-bit "user electronic signature" (UES). Programming is accomplished one row at a time by serially shifting a 6-bit row address and 132 bits of program data bits into address/data shift register 102 through the SDI terminal. The 6-bit row address specifies which of the 44 rows of the  $_{20}$ AND array, or the 64-bit UES, is to be programmed. The 132 bits of programming bits are then provided to implement the desired configuration of the AND array at the specified row or the UES. An 8-bit ID shift register and a 20-bit architectural shift register 104 are provided, respectively, for storing 25 eters can be properly handled by programming command an identification pattern and for specifying configuration information of the ispGAL22V10 device.

FIG. 2 shows the array map of an ispLSI 1016 device. As shown in FIG. 2, an ispLSI 1016 device includes a 96×160bit E<sup>2</sup>CMOS (Electrically erasable Complementary Metal- 30 Oxide Semiconductor) cell array 201. As in the ispGAL22V10 device, cell array of the ispLSI 1016 device is programmed row by row. However, instead of specifying a multi-bit address, a 96-bit address shift register 202 is provided. Each bit in address shift register 202 corresponds 35 to a 160-bit row in cell array 201. A 160-bit data register 203, divided into 80-bit (half-row) high order register 203a and 80-bit low order shift register 203b, is provided for holding the program data bits. Since separate commands are required to load or read each half-row in data register 203 (i.e. a 40 500 provides the name of the JEDEC file containing a separate command is required for loading each of data registers 203a and 203b), for the purpose of the remaining discussion, the data input and output unit of ispLSI 1016 device can be considered to be the 80-bit half-row. To program the ispLSI 1016 device, a single '1' bit is shifted 45 into address shift register 202. The position of the single '1' bit in address shift register 202 indicates the row to be programmed. Programming is carried out by two program instructions, "PRGMH" (program high half-row) or "PRGML" (program low half-row), each instruction writes 50 a half-row program data bits in the corresponding one of data registers 203a and 203b into the corresponding halfrow at the address indicated by the single '1' bit in address register 202. An 8-bit ID shift register 204 is provided for holding an 8-bit identification code. 55

Programming an ispLSI 1032 device is similar to programming the ispLSI 1016 device described above with respect to FIG. 2. FIG. 3 shows the array map of an ispLSI 1032 device. An ispLSI 1032 device includes a 108 by 320-bit E<sup>2</sup>CMOS array 301. Thus, the ispLSI 1032 device 60 includes a 108-bit address shift register 302 and a 320-bit data register 303, which is divided into higher order half-row data register 303a and low order half-row data register 303b. Again, since separate commands are required for loading or reading each of half-row data registers 303a and 303b, the 65 input and output unit for data transfer in such the ispLSI 1032 device is 160 bits.

6

The method of the present invention first creates in memory an "ispSTREAM" file, which is a file containing both programming instructions and data, in the order the programming instructions and the data are subsequently used to program the ISP PLDs simultaneously. The steps for creating such a file are illustrated by FIG. 14. Step 1401, which represents a subroutine "pack\_jedec\_file" in the source code provided in Appendix A, begins compilation of the ispSTREAM file by invoking a subroutine "dl\_read\_ dldfile" is represented by step 1402. At step 1402, a configuration description file (identified by the ".dld" file extension) is read. An example of such a configuration description file is shown in FIG. 5. As shown in FIG. 5, each line corresponding to one device in the serial chain 400 of FIG. 4 to be programmed. On each line of configuration description file 500 is provided three fields, which correspond to a (i) device field, (ii) a programming directive field, and (iii) a programming bit pattern field (i.e. the name of a "JEDEC file"). JEDEC is an industry standard format for specifying test vectors known to those skilled in the art. The device field identifies the type of the device to be programmed, so that device-specific commands and paramgenerator 404. In FIG. 5, configuration description file 500 specifies 22V10 (i.e. the ispGa122v10 device), 1016 (an ispLSI device with 16 generic logic blocks) and 1032 (an ispLSI device with 32 generic logic blocks). At present, four types of programming directives are used: (i) "PV", which indicates both programming and verification are to be performed; (ii) "NOP", which indicates no operation; (iii) "V", which indicates only verification is to be performed, and (iv) "E", which indicates only the function "erase" is to be performed. Verification involves reading the programming data from a programmed logic device and comparing the data thus read-back with the expected bit pattern. The function "erase" erases all programming from a ISP PLD.

The "JEDEC file" field of configuration description file programming bit pattern for use by Programming command generator 404 when carrying out the specified programming directive. In addition, step 1402 (FIG. 14) identifies, for each device listed on the configuration description file 500, the number of rows and the size in bit number of each row. Step 1402 also identifies which of the devices in the serially connected chain 400 has the largest number of programmable units, defined as the largest number of rows in the ispGAL22V10 type devices, or the largest number of halfrows in the ispLSI type devices, whichever is larger.

Upon completion of Step 1402 described above, step 1403 is invoked to calculate a "composite array map". The present invention considers serially connected chain 400 as if it is a device having a number of rows equal to the largest number of programmable units, as identified in step 1402 above. For example, the serially connected chain of FIG. 4 is considered a device having (i) 45 rows (rows 0-44) of 378 bits; (ii) one row (row 45) of 260 bits, (iii) 146 (rows 46–191) of 240 bits, and (iv) 24 rows (rows 192–215) of 160 bits. FIG. 9 illustrates this composite array map for the serially connected chain 400 of FIG. 4. As shown in FIG. 9, in rows 0-44, one row from ISP PLD 401 and two half-rows from each of the ISP PLDs 402 and 403 can be programmed simultaneously. Thus, the total number of bits programmed in each of rows 0-44 would be the sum of 138 bits, 80 bits and 160 bits, i.e. 378 bits. Row 45 represents the programming of the 20 architectural bits and one half-row each of

ISP PLDs 402 and 403. Thus, the number of bits to be programmed in row 45 is the sum of 20, 80 and 160, i.e. 260 bits. For rows 46-191, since ISP PLD 401 does not have these rows, the number of bits to be programmed is the sum of two half-rows of ISP PLDs 402 and 403. Thus, the number of bits programmed in rows 46-191 is the sum of 80 and 160, i.e. 240 bits. Finally, in rows 192-215, only ISP PLD 403 need to be programmed. Hence, the number of bits to be programmed in rows 192-215 is one half-row of ISP PLD 403, i.e. 160 bits.

According to this composite array map, a bit stream file ("ispSTREAM file") is created in memory. The isp-STREAM file holds the bit stream data necessary to shift data and instructions into the serially connected chain of ISP PLDs (e.g. serially connected chain 400 of FIG. 4) to be 15 programmed. FIG. 10b shows the format of an ispSTREAM file 1000 for the serially connected chain 400 of ISP PLDs 401-403 of FIG. 4.

To build ispSTREAM file 1000, the memory cells required for the ispSTREAM file is allocated. To perform 20 this allocation, the procedure outlined in the flow diagram 1600, which is shown in two portions 1600a and 1600b in FIGS. 16a and 16b, is used. In FIG. 16a, step 1602 allocates 24 bits. These 24 bits are provided to contain the three 8-bit ID code for each of ISP PLDs 401, 402 and 403. At step 25 1603, 15 bits are allocated for holding a 5-bit instruction of each of ISP PLDs 401, 402 and 403 for a bulk erase instruction. The instruction sets executable by the state machines of the ispGAL22V10 type devices (e.g. ISP PLD 401) and the ispLSI type devices (e.g. ISP PLDs 402 and  $_{30}$ 403) are shown in FIGS. 10c and 10d respectively. FIGS. 10c and 10d provide, for each instruction, the opcode for the instruction, a mnemonic of the instruction and a short description of the function of the instruction. As shown in FIG. 10b. for example, the bulk erase instruction in an 35 ispLSI type device has an opcode '00011' (binary) and an mnemonic "UBE". The UBE instruction erases the programming in the entire device by setting all the programmable bits to a binary '1'.

Then, at step 1604, 15 bits (bits 1003) are allocated for 40 shifting into ISP PLDs 402 and 403 the 5-bit "ADDSHFT" instruction (FIG. 10c), and shifting into ISP PLD 401 the 5-bit "FLOWTHRU" (or "PASS") instruction. The FLOWTHRU instruction is provided ISP PLD 401 because an ispGAL22V10 type device does not have an address 45 register, address being specified as the first 6 bits of data register 103. Then, 204 bits (bits 1004) are allocated, at step 1605 for the actual address bits to be shifted in the address registers 202 and 302 of ISP PLDs 402 and 403, respective. Since ISP PLDs 402 and 403 have 96 and 108 rows, 50 respectively, the total number of bits allocated in bits 1004 for the actual address bits of ISP PLDs 402 and 403 is 204. At step 1606, 15 bits (bits 1005) are allocated for the data shifting instructions ("DATASHFT" or "SHIFT\_DATA" in FIGS. 10c and 10d) for shifting data bits into data registers 55 102a, 203a and 303a. Then, at step 1607, a number of bits (bits 1006) are allocated for data to be shifted into in the first row (i.e. row 0) of composite array 900 (FIG. 9) constructed above. In the embodiment of FIG. 4, as explained above, row 0 includes 378 data bits, including 6 address bits and 60 132 data bits for ISP PLD 401, 80 data bits for ISP PLD 402 and 160 data bits for ISP PLD 403. In the next two steps, i.e. steps 1608 and 1609, 30 bits (bits 1007 and 1008) are allocated for the program instructions ("PROGRAM" and "VERIFY") used in programming ISP PLDs 401-403. PRGMH and VER/LDH are instructions which program and

verify, respectively, using data in the higher half-row portion of the data registers of the ispLSI devices (e.g. half-row data registers 203a and 303a). Step 1610 allocates 15 bits (bits 1010) for holding the "DATASHFT" and "SHIFT\_DATA" instructions for shifting data out of data registers PLD ISPs 402 and 403, and ISP PLD 401 respectively. Steps 1611-1615 (steps 1612-1615 shown in FIG. 16b) are steps corresponding to steps 1606-1610 described above. Steps 1611-1615 are provided for processing the next row of ISP PLD 401 and the lower 160-bit and 360-bit half-rows of ISP 10 PLDs 402 and 403, at the address specified by address registers 202 and 302, respectively. Steps 1611-1615 allocate in the ispSTREAM file structures 1010-1014. Steps 1604–1615 are repeated for rows 2 to 215 of composite array map 900 until row 215 (see FIG. 9) is processed. This repetitive loop and the termination decision point are represented by decision point 1616. For row 45, the data bits allocated for step 1612 is 260, as discussed above. Similarly, for rows 46-191 the data bits allocated for steps 1607 and 1612 are 240 bits. For rows 192-215, the data bits allocated for steps 1607 and 1612 are 160 bits. For rows 192-195, since all rows in ISP PLD 402 are programmed, the number of bits allocated for the address bits of step 1605 is 108, which is the number of rows for ISP PLD 403.

Referring back to FIG. 14, upon allocation of isp-STREAM file 1000, step 1403 is completed. Then, the next step, i.e. step 1404 (execution of subroutine "pack\_jedec\_ files" continues), invokes a subroutine "read\_jedec\_files". Step 1404 reads the JEDEC files referenced in configuration description file 500 one by one, and converts the information in each JEDEC file (provided in ASCII characters) into a packed binary map in memory, organized row by row. As each JEDEC file is read, each row (for ispGAL22V10 type device) or half-row (for ispLSI type device) that is all '1's (i.e. all program bits in the row are binary '1's) is marked. In a preferred embodiment, after all program bits in the JEDEC file are read into the packed binary map in memory, the rows or half-rows in the packed binary map are sorted. In ispGAL22V10 devices, the rows are sorted such that the rows that are not all binary '1's are arranged in ascending address order, followed by the all '1's rows in ascending address order. In ispLSI devices, the rows are sorted in the data structure in the order: 1) in ascending address order, all rows which are not all '1's in both the higher and the lower half-rows of an address; (ii) in ascending address order, all rows which have all '1's in one of the half-rows, and not all '1's in the other half-row; and (iii) in ascending address order, all rows which are all '1's in both half-words.

FIGS. 6, 7 and 8 are JEDEC files illustrative of the JEDEC files referenced in FIG. 5 for ISP PLDs 401, 402 and 403 respectively. As shown in FIG. 6, a JEDEC file for an ispGAL22V10 device reads program bits from a 44×132-bit array 601. Each column of bit array 601 corresponds to the 132 programming bits for a row in the AND array 101 of FIG. 1. In combination with a 6-bit address generated by programming command generator 404 (FIG. 4), these 132 bits programming bits are shifted into address/data shift register 102 to program a row of AND array 101. The remaining portions of the JEDEC file provides information such as the 20 architectural bits, and the 64-bit UES. The format for a JEDEC file used with an ispGAL22V10 device is known to one skilled in the art.

FIG. 7 shows a JEDEC file for an ispLSI 1016 device, illustrative of the "1016.jed" file referenced in FIG. 5 for ISP "PRGMH") and the verify instructions ("VER/LDH" or 65 PLD 402 of FIG. 4. As shown in FIG. 7, program bits are read by Programming command generator 404 from a 192×80-bit array 701. Unlike array 601, i.e. the program bits

array of a JEDEC file for an ispGAL22V10 device, where each column represents a row of programmable components in the device, every two rows of array 701 represent the program bits for either the higher order half-row or the lower order half-row of a corresponding row in the  $E^2$ CMOS array -5 of the ispLSI device. Programming is achieved when the program bits are downloaded, by executing the appropriate programming command, onto the target ISP PLD from data registers 203a and 203b. FIG. 8, which shows a JEDEC file illustrative of the JEDEC file "1016.jed" referenced in FIG. 10 5 for ISP PLD 402, contains a 108×160-bit array 801 which is interpreted in the same manner as array 701 of FIG. 7. Of course, every two rows in array 801 has 160 bits, corresponding to either the 160-bit higher order half-row, or the 160-bit lower order half-row, for a 320-bit row of the 15 E<sup>2</sup>CMOS array 201 of a ispLSI 1032 device. As an example, FIG. 7 shows that the higher order half-row of program bits at address 7 is all '1's. Similarly, FIG. 8 shows that both half-rows of the program bits at address 64 are all '1's. The next step in step 1404 is to fill actual program and command 20 data into the ispSTREAM file 1000. The procedure for filling ispSTREAM file 1000 is provided as procedure 1700 in FIGS. 17a and 17b.

FIGS. 17a and 17b are portions 1700a and 1700b of procedure 1700 respectively. FIG. 17a shows, on the left 25 hand side, steps 1701-1710 taken to fill program data into ispSTREAM file 1000 and, on the right side, the actual program bits which are filled into data structures 10011-1019 of ispSTREAM file 1000 shown in FIG. 10b. FIG. 17b shows, on the left hand side, steps 1711-1717 taken to fill 30 program data into ispSTREAM file 1000 and, on the right side, the actual program bits which are filled into data structures 1011-1014 of ispSTREAM file 1000 shown in FIG. 10b. Initially, as shown in FIG. 17a, program bits related to the last device in serially connected chain 400 is 35 first processed. Thus, at step 1701, the 8-bit ID code filled the last 8 bits in data structure 1001 of ispSTREAM file 1000. Then, at the step 1702, the "UBE" instruction (user bulk erase) is entered into the corresponding 5 bits (i.e. the last 5 bits) of data structure 1002. The opcode corresponding 40 to the "ADDSHFT" (address shift) instruction is then, at step 1703, entered into the last 5 bits of data structure 1003. The address bits to be shifted into address register 302 are provided in the last 108 bits of the data structure 1004. The opcode corresponding to the "DATASHFT" (data shift) 45 instruction is then provided, at step 1705, to the last 5 bits of data structure 1005. Then, at step 1706, 160 program data bits, corresponding to the higher order half-row of the first row in the packed binary map for ISP PLD 403, are provided to the last 160 bits of the data structure 1006. At steps 1707 50 and 1708, the opcodes for "PRGMH" (program higher order half-row) and "VER/LDH" (verify or load higher order half-row) are provided into the corresponding bits of data structures 1007 and 1008. At step 1709, the opcode for the "DATASHFT" instruction is provided in the corresponding 55 bits of data structure 1009. This "DATASHFT" instruction will be used to shift out the higher order half-word of ISP PLD 403, at the address specified in address register 303, for verification. The steps 1710-1714 provide, for the lower half-row of an ispLSI device, steps for filling the instruction 60 opcodes and program data bits in data structures 1010-1014. Step 1715 tests if the command and program data bits for all rows of ISP PLD 403 are provided to ispSTREAM file 1000. If not all instructions and program data bits of ISP PLD 403 are provided to ispSTREAM file 1000, process 1700 repeats 65 steps 1703-1714, until done. When all instructions and program data bits of this last device in serially connected

chain 400 are provided to ispSTREAM file 1000, the next JEDEC file in configuration description 500 is read. Steps 1701–1715 are then repeated for filling in actual command and program data bits in ispSTREAM file 1000 corresponding to the next device in the serially connected chain 400 of FIG. 4. Process 1700 continues until commands and program data bits for all devices in serially connected chain 400 are provided into ispSTREAM file 1000. The result of process 1700 on serially connected chain 400, using program data bits from FIGS. 6–8, are shown in FIG. 10b. At this point, the subroutine "pack\_jedec\_files" is completed.

Simultaneous programming for the devices in the serially connected chain 400 can proceed then from the ispSTREAM file 100 thus filled. In this embodiment, a procedure "ispstream\_pump" is provided for performing programming and verification from the ispSTREAM file. The ispstream\_pump procedure is provided in source code form in Appendix A. A hardware and software system which is capable of downloading the output data of the ispstream\_\_\_\_ pump procedure for programming and verification in the devices of the serially connected chain is described in the ISP Manual 1994 referenced above. In particular, the hardware and software system and the operational procedures for operating such a system are discussed in Chapter 3 of the ISP Manual 1994, entitled "In-System Programming on a PC or Sun Workstation". The teachings of ISP Manual 1994 are hereby incorporated by reference in it's entirety.

Specifically, a procedure for processing and downloading the data of ispSTREAM file 1000 to target devices in the serially connected chain 400 of FIG. 4 is illustrated in the flow diagram 1500, which is shown in 5 portions 1500a-1400e in FIGS. 15a-e. FIG. 15a shows a portion 1500a, including steps 1501-1507 of process 1500. As shown in FIG. 15a, at step 1501, the subroutine "ispstream\_ pump" is invoked to begin the process of processing and downloading data from ispSTREAM file 1000 to the target devices of serially connected chain 400 of FIG. 4. The subroutine "ispstream\_pump" calls at step 1502, a subroutine "move\_to\_id\_state", which causes all devices in the serially connected chain 400 to go into idle state. Idle state is entered when Programming command generator 404 (FIG. 4) provides the following signal protocol: (i) setting ispEN, SDI, SCLK and MODE signals each to logic low; (ii) following (i), setting MODE signal to logic high; (iii) following (ii), pulsing signal SCLK; and (iv) following (iii), resetting MODE signal to logic low.

FIG. 18a shows the states of the three ID registers 104, 204 and 304 in ISP PLDs 401, 402 and 403 of serially connected chain 400. At step 1503, command program generator 404 is caused to pulse the SCLK signal 24 times, so as to output as the values of signal SDO the respective ID codes of ISP PLDs 401, 402 and 403. These ID codes are then compared with the ID code values in data structure 1001 of ispSTREAM file 1000. At step 1504, the ispstream\_pump subroutines calls the subroutine "execute ()" to place the devices in serially connected chain 400 into the "shift" state. The shift state is entered by causing command program generator 404 to execute the protocol: (i) setting ispEN, SDI, SCLK, MODE signals at logic low; (ii) thereafter, setting MODE and SDI signals to logic high; (iii) pulsing the SCLK signal once, and (iv) bringing the MODE and SDI signals to logic low. In the "shift" state, an in-circuit programmable device is ready to receive instructions for executing a command in a command register of the in-circuit programmable device.

At step 1505, the instructions for bulk erase, i.e. "BULK\_ ERASE", for an ispGAL22V10 type device and "UBE", for an ispLSI type device, are taken from data structure 1002 of ispSTREAM file 1000 and downloaded through signal SDI into ISP PLDs 401, 402 and 403, by pulsing the SCLK signal 15 times. Next, at step 1506, the devices of serially connected chain 400 are placed into the "execute" state by 5 Programming command generator 404, executing the signal protocol illustrated in FIG. 11. The bulk erase function is then executed at step 1507 by setting ispEN, SDI, SCLK and Mode signals logic low and then pulsing signal SCLK.

FIG. 5b shows portion 1500b of flow diagram 1500, 10 which covers steps 1508-1515. Step 1508 is a waiting step to wait for the completion of the bulk erase instruction. Since ISP PLDs devices 401, 402 and 403 are bulk-erased simultaneously, waiting step 1508 is completed when bulk erase is completed in the device requiring the most time. At 15step 1509, ISP PLDs 401, 402 and 403 are placed again in "shift" state, in the manner described above, for receiving further instructions. At step 1510, the shift address instructions (i.e. the "ADDSHFT" instruction for each of ISP PLDs 402 and 403 and the "FLOWTHRU" instruction for ISP  $^{20}$ PLD 401, as discussed above) are then retrieved from data structure 1003 of ispSTREAM file 1000 and downloaded into ISP PLDs 401, 402 and 403. FIG. 18b shows the contents of 5-bits instruction registers 105, 205 and 305 of ISP PLDs 401-403, respectively, after the shift address <sup>25</sup> instructions are downloaded. At step 1511, ISP PLDs 401, 402 and 403 are placed in the "execute" state in the manner described above. The addresses bits (204) are then retrieved, at step 1512, from data structure 1004 of ispSTREAM file 1000 and shifted into ISP PLDs 402 and 403, by pulsing the 30SCLK signal 204 times. FIG. 12 is a schematic diagram showing shifting address bits into shift address registers 202 and 302.

At steps 1514–1516 (FIG. 15c), the shift data instruction and programming data bits are retrieved from data structures <sup>35</sup> 1005 and 1006, and shifted into data registers 103, 203a and 303a of ISP PLDs 401, 402 and 403. Steps 1514-1516 perform, respectively, the functions of (i) placing ISP PLDs 401-403 in "shift" state, (ii) shifting in the data shift 40 instructions of data structure 1005, (iii) placing ISP PLDs 401-403 in "execute" state, (iv) shifting the program data bits of data structure 1006 into data registers 103, 203a and 203b. FIG. 13 shows the contents of data registers 103, 203a and 303a, after the step 1516. ISP PLDs 401-403 are then 45 placed in "shift" mode again to receive the program instructions. If the data shifted into data registers 103, 203a and 303a are all '1's, programming can be skipped. Thus, at step 1518, if the data in data registers 103, 203a and 303a are all '1's, the next step is step 1524 (FIG. 15c); otherwise, step 50 1519 retrieves from data structure 1007 of ispSTREAM file 1000 the program instructions for ISP PLDs 401-403. At step 1520, ISP PLDs 401-403 are then placed into the "execute" state, in the manner explained above. Programming is initiated at step 1521 by setting ispEN, MODE, SDI 55 and SCLK signal to logic low and then pulsing the SCLK signal. State 1522 is a timing state, in which command generator 404 waits a predetermined required time period to

ensure successful programming. Thus, simultaneous programming is achieved. ISP PLDs 401-403 are then returned to the shift state for receiving further instructions. FIG. 18c shows the contents of 5-bits instruction registers 105, 205 and 305 of ISP PLDs 401-403, respectively, after the shift address instructions are downloaded at step 1519. FIG. 18c also shows that, when the program bits in data register 203a is all '1's, but if neither data register 103 nor data register 303a is all '1's, then programming proceeds with ISP PLD 402's instruction register 205 set to a NOP (no operation) instruction. It is found that, with the sorting at step 1404 of programming data bits into the two groups, for an ispGAL22V10 type device, and three groups, for an ispLSI device, substantial programming time is saved because programming steps 1519-1523 can then be skipped.

Verify instructions are then retrieved from data structure 1008 of ispSTREAM file 100 and provided to ISP PLDs 401-403 at step 1524. At step 1525, ISP PLDs 401-403 are placed in the "execute" state. At step 1526, data verify operations are initiated by the protocol: (i) setting ispEN, SDI, SCK, and MODE signals to logic low and (ii) thereafter, the SCLK clock signal is pulsed. State 1527 then waits for a period sufficient for each ISP PLD device to read the memory for programmed data bits stored at steps 1519-1523. The data to be verified are then shifted out of data registers 103, 203a and 203b by (i) placing, at step 1528, ISP PLDs 401-403 into the "shift state; (ii) at step 1529, retrieving from data structure 1014 of ispSTREAM file 1000 the data shift instructions, and shifting such instructions into ISP PLDs 401-403; (iii) at step 1530, placing ISP PLDs 401-403 into the "execute" state, and (iv) at step 1531, pulsing signal SCLK 378 times to output at signal SDO, the data bits of data registers 103, 203a and 303a. If the data shifted out of ISP PLDs 401-403 are identical to the data in data structure 1006 of ispSTREAM file 1000, ISP PLDs 401-403 are properly programmed.

At step 1532 (FIG. 15*e*), ISP PLDs 401-403 are placed in the "shift" state to continue programming of ISP PLDs 401-403. Steps 1514-1532 are repeated to program the next row in ISP PLD 401, and the next half-row in each of ISP PLDs 402-403. Thereafter, at decision point 1534, isp-STREAM file 1000 is checked to determined all data in ispSTREAM file 1000 have been downloaded into the devices in serially connected chain 400. If there remains more data to download into ISP PLDs 401-403, procedure 1500 returns to step 1514; otherwise, procedure 1500 is completed.

The above detailed description is provided to illustrate specific embodiments of the present invention and is not intended to be limiting. Numerous variations and modifications within the scope of the present invention are possible. For example, as mentioned above, the present invention is applicable to all types of field programmable devices, including programmable logic devices, programmable memories, and programmable analog circuits. The present invention is set forth in the claims appended below.

14

HESHILLY A. DL ZOOM.C This program contains the core functions needed to perform the daisy chain parallel programming. Rev Date Description By 5.30 Howard Tang 11/09/94 \*\*\*\*\*\*\*\*\*\*\* #include <stdio.h>

#include <conio.h> #include <math.h> #include <dos.h> #include <alloc.h>\*\* #include <process.h> #include <stdlib.h> #include <bios.h>

#include <direct.h> #include <time.h> #include <string.h>

#include <ctype.h> #include "dl\_com.h" #include "dl\_down.h"